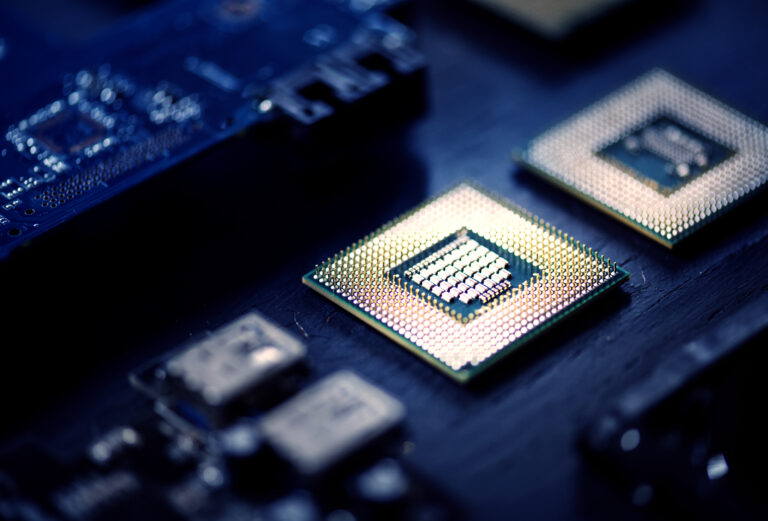

Microprocessor architectures lie at the core of computing. In this post, I share my thoughts on how these systems have evolved and why they matter today. While I’m not a hardware engineer, I’ve always been fascinated by how these tiny chips shape our digital lives.

As the tech world rapidly evolves, software often takes center stage—with better accessibility, reusability, and community support. In contrast, hardware development remains more closed, largely because microprocessor architectures and instruction sets are usually proprietary. That makes innovation harder and sharing limited.

In this article, we’ll explore the fundamentals of microprocessor design, the RISC vs CISC debate, and newer trends like ARM and RISC-V.

What Are Microprocessor Architectures?

A microprocessor architecture defines how a CPU is built and how its components interact. Acting as the brain of any computing system, a CPU is made up of several critical parts:

Key Components of a Microprocessor

🔸 Registers

Registers are the CPU’s fastest and smallest memory units. They enable quick access to instructions and data. Types of registers include:

MAR (Memory Address Register)

MBR/MDR (Memory Buffer/Data Register)

PC (Program Counter)

🔸 Control Unit (CU)

The CU acts like a traffic controller. It fetches instructions from memory, decodes them, and then routes them to the appropriate components for execution.

🔸 Arithmetic Logic Unit (ALU)

The ALU performs all math and logic operations. It takes input from registers, processes the instructions, and sends the result back for further use.

CISC Architecture: Complexity Made Easy for Developers

CISC (Complex Instruction Set Computer) processors use complex instructions to perform multiple tasks in one command. This reduces the number of instructions a program needs, which was beneficial when memory was limited and expensive.

🔑 Key Features of CISC:

100–200 complex instructions

Multi-cycle execution

Variable-length instruction formats

Advanced addressing modes

Hardware-heavy complexity

Shorter code, more energy usage

CISC made programming easier by shifting complexity to the CPU. It remains dominant in desktops and servers, especially with x86 architecture.

RISC Architecture: Simplicity for Speed

RISC (Reduced Instruction Set Computer) processors simplify the instruction set. Each instruction does just one thing, but very quickly. This makes the CPU easier to build and more energy-efficient.

🔑 Key Features of RISC:

30–40 simple instructions

Single-cycle execution

Fixed-length instruction formats

Emphasis on compiler optimization

More registers, larger codebase

Software-focused complexity

RISC has gained momentum with the rise of smartphones, IoT devices, and energy-efficient systems.

Performance Metrics in Microprocessor Architectures

To compare microprocessor architectures, we often use this formula:

CPU Time = Instruction Count × Cycles per Instruction × Clock Cycle Time

Instruction Count: RISC usually has more due to simpler commands.

CPI (Cycles per Instruction): Lower in RISC systems due to single-cycle execution.

Clock Cycle Time: Shorter cycles mean faster performance, but higher heat and power usage.

The balance between these variables defines how efficient and powerful a processor is.

Comparing x86 and ARM Architectures

Two industry titans dominate the CPU world:

🖥️ x86 (CISC-based):

Found in most desktops and gaming systems

Backed by Intel and AMD

Decades of backward compatibility

📱 ARM (RISC-based):

Powers mobile phones and tablets

Energy-efficient, scalable design

Gaining ground in laptops (e.g., Apple Silicon)

Apple’s transition from Intel (x86) to its own ARM-based M-series chips is a major signal of ARM’s growing role in high-performance computing.

RISC-V: The Open-Source Future of Microprocessor Design

RISC-V is an open-source alternative to ARM. Its instruction set is royalty-free and customizable, which makes it ideal for:

Startups

Academia

National security initiatives

While it may not replace ARM or x86 entirely—just as Linux didn’t replace Windows—it enables affordable, flexible chip design without legal hurdles.

Geopolitics and Chip Independence

Microprocessors are no longer just tech—they’re strategic assets.

The U.S. ban on Huawei exposed China’s dependency on foreign tech.

India, Russia, and China are now investing heavily in domestic chip design.

The global chip shortage revealed just how fragile the supply chain is.

This has intensified interest in open architectures like RISC-V and encouraged local production efforts.

Looking Ahead: RISC on the Rise

RISC-based architectures (ARM and RISC-V) are catching up fast. With growing demand for energy-efficient systems, expect to see:

More servers and desktops using RISC-based chips

ARM competing head-to-head with x86

RISC-V adopted in more niche and innovative applications

Still, CISC will remain relevant in legacy systems, gaming, and high-performance use cases.

Final Thoughts

Microprocessor architectures are evolving rapidly. Understanding the difference between RISC, CISC, x86, ARM, and RISC-V can help you better grasp the future of computing—from mobile devices to data centers.

To explore how our software solutions interact with modern processor architectures, check out our web development services.

Have thoughts or questions on processor trends? Contact us. Let’s talk.